Universal Verification Methodology based verification for Memory Controllers in System on Chip

Tan Thien Bao

Nguyen Phuong Uyen

Luong Quoc Lan

Nguyen Dai Thinh

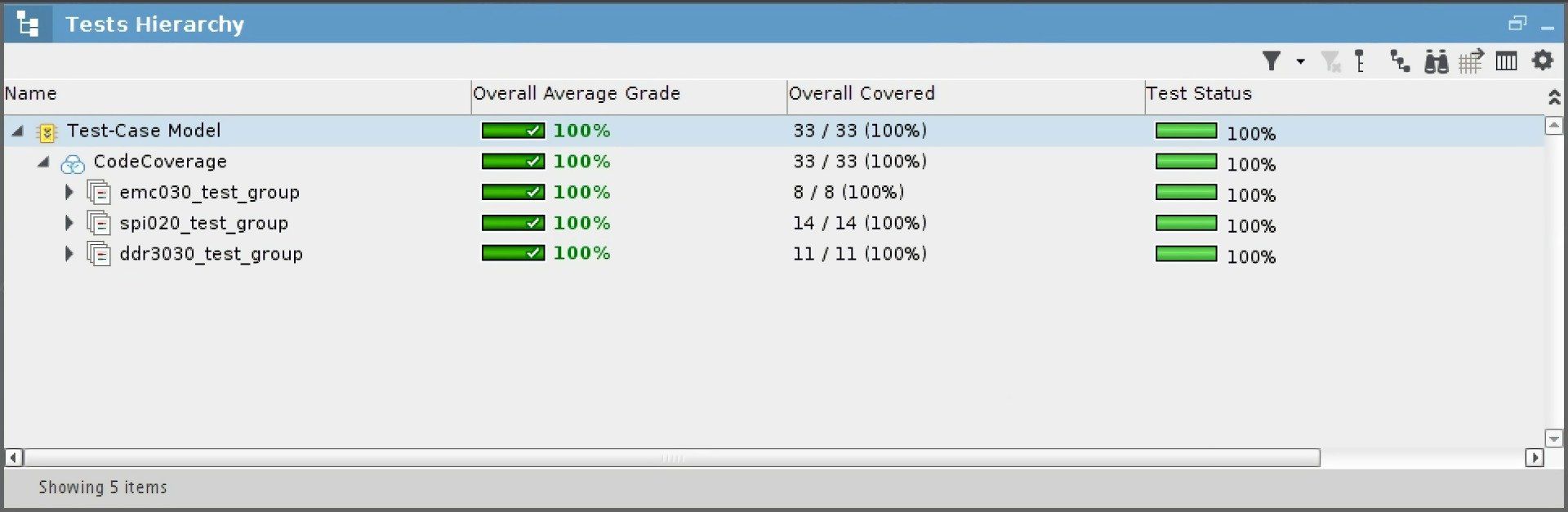

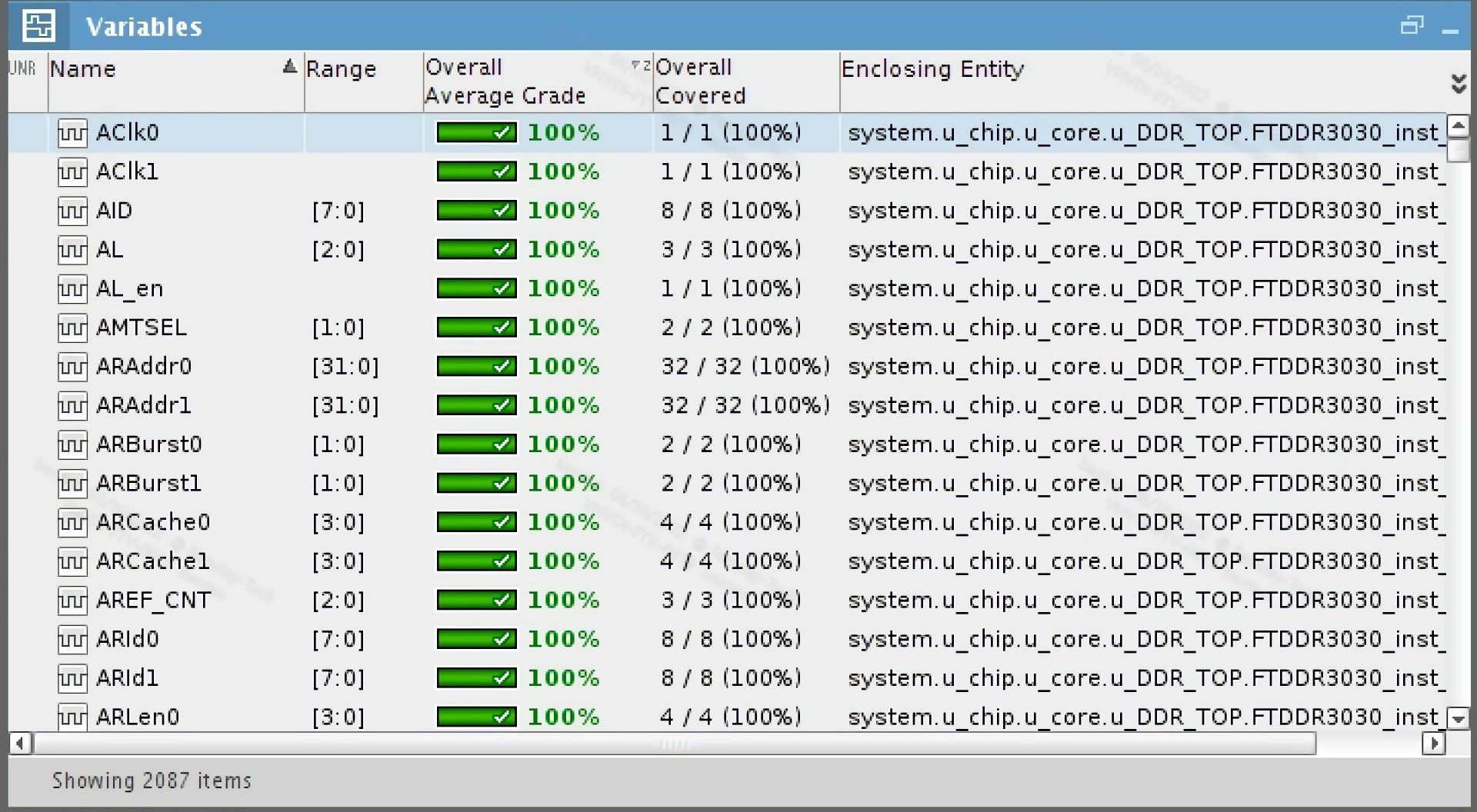

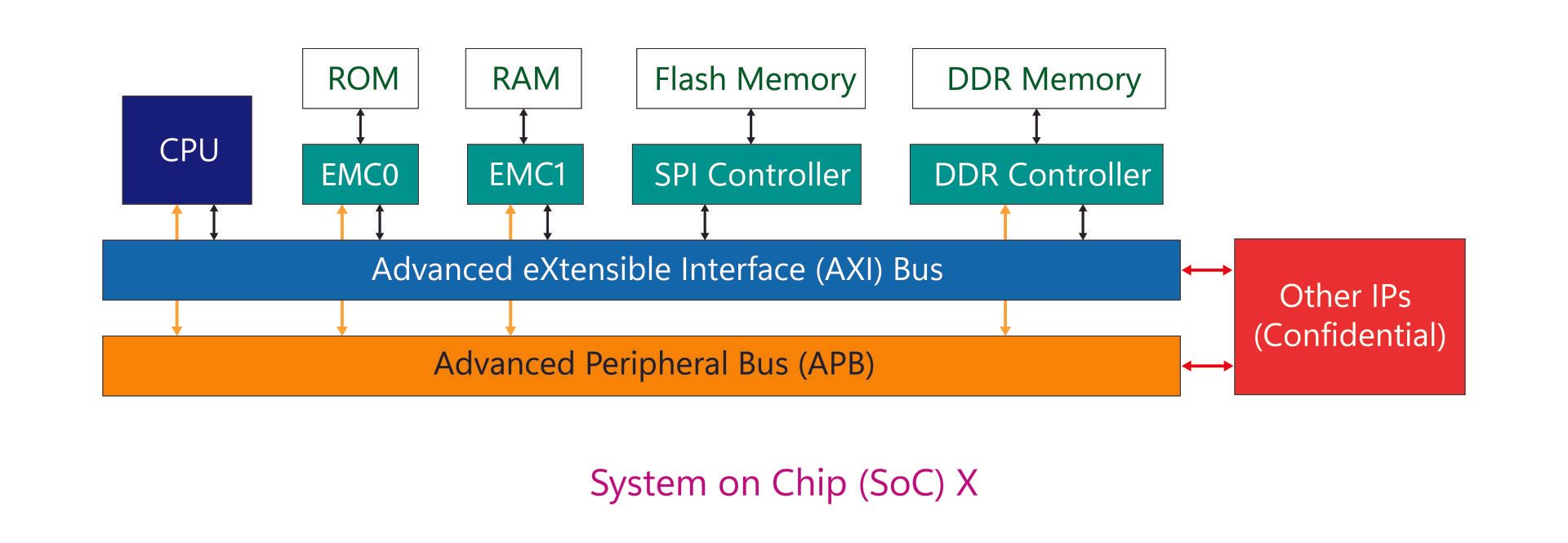

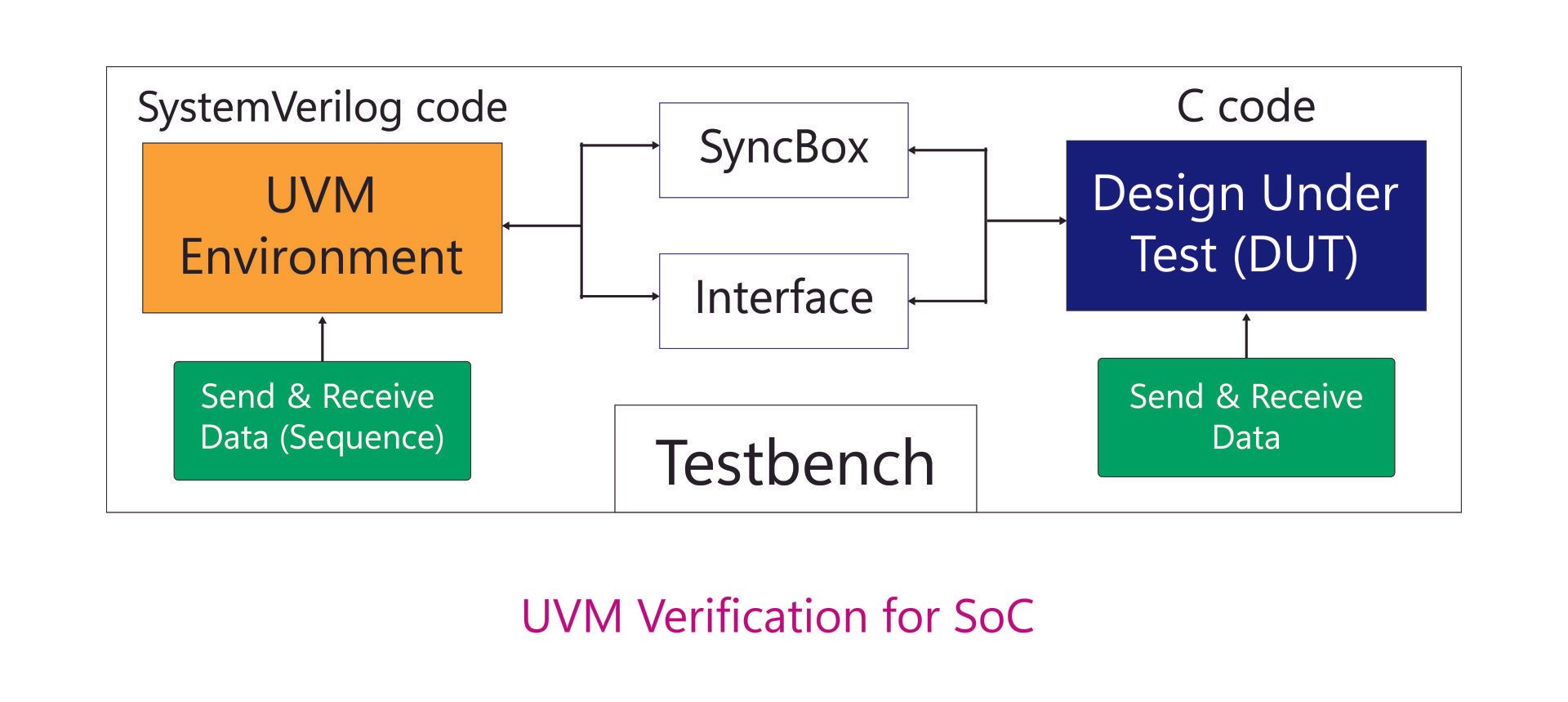

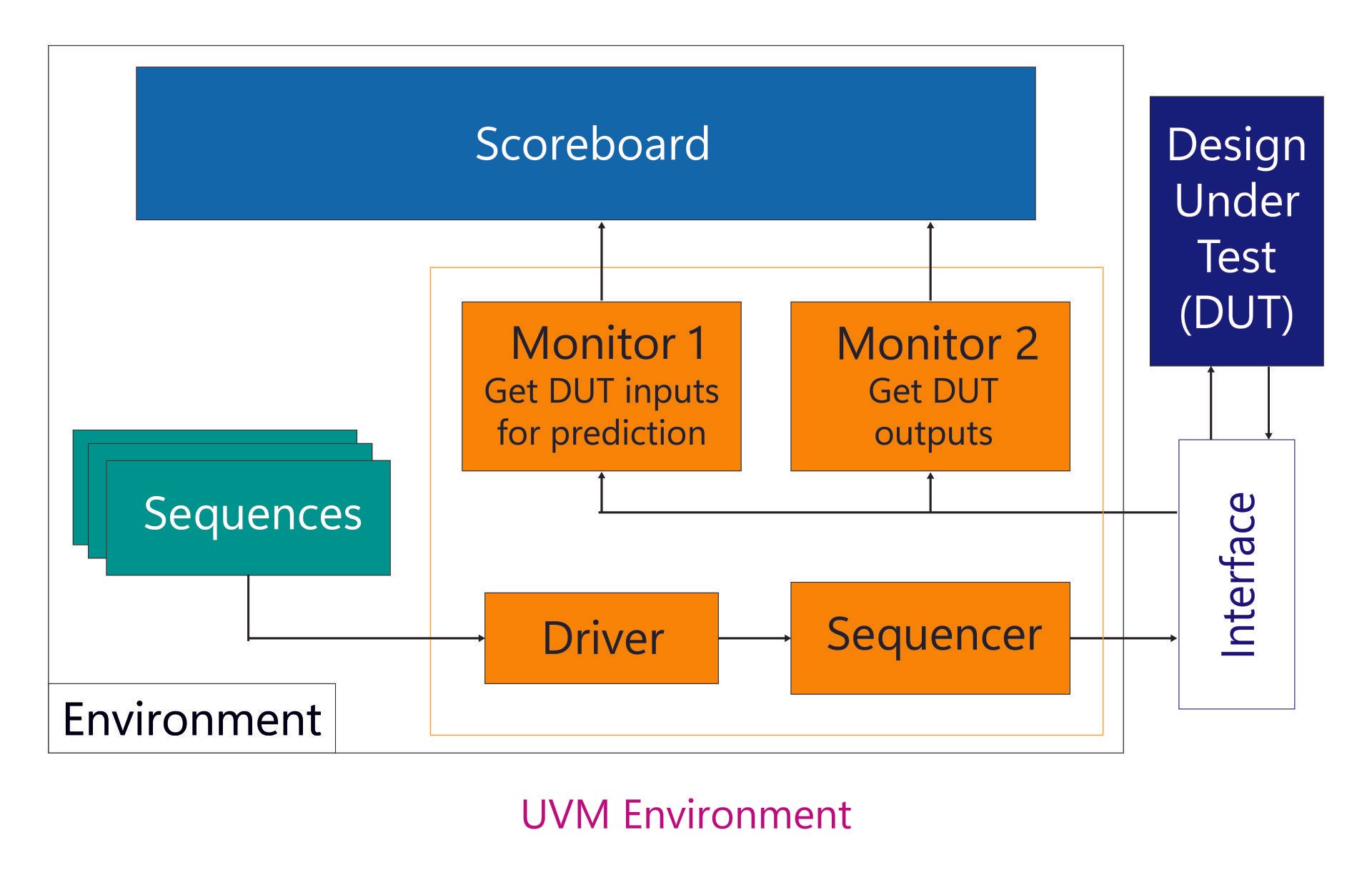

Under the supervision of Faraday Technology Vietnam, the project focuses on the three types of memory controller IPs in System on Chip X: Embedded Memory Controller, SPI Flash Controller and DDR Controller. The goal is to design a Universal Verification Methodology (UVM) based verification to test their function according to the provided specification. To evaluate the success of the project, all tests must achieve 100% functional coverage and accuracy, which means all the functions of IPs are verified and error-free.

In the System on Chip, Functional Memory Controllers ensure the operation of Memories and the system's overall performance. Therefore, a successful testing process will be beneficial for the whole SoC design process. Moreover, the verification environment built in this project can be used in future projects with minimum adjustment, thanks to UVM features and characteristics: modularity, reusability, scalability and flexibility.

Demo Video