Low-noise Local Oscillator for 5G Transceivers

The rollout of 5G networks requires communication systems that are faster, more reliable, and more power-efficient than ever before. At the heart of every wireless device is a local oscillator (LO) - a circuit that generates the reference signal used to keep communication channels synchronized. If this signal contains too much noise, it can blur or distort transmitted information, reducing the quality of the connection. Designing an LO with very low noise is therefore critical for 5G applications.

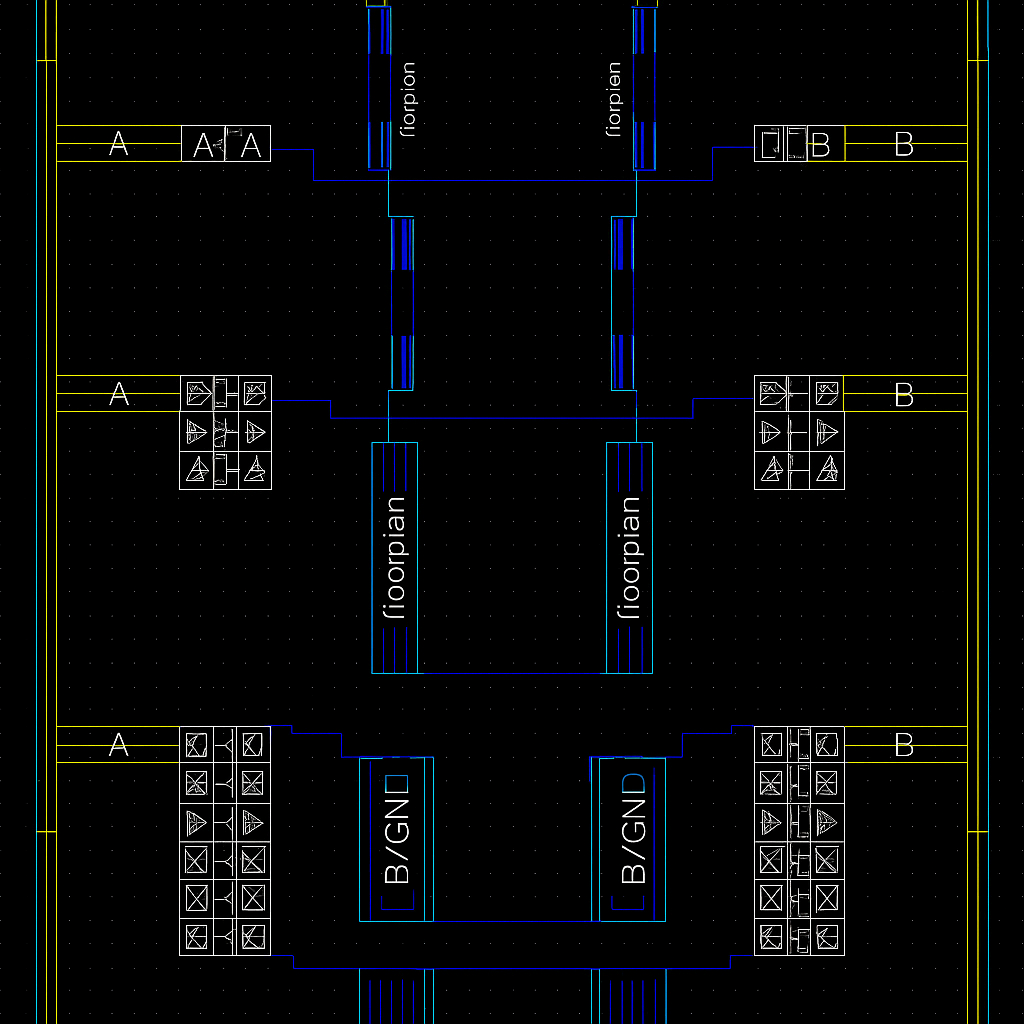

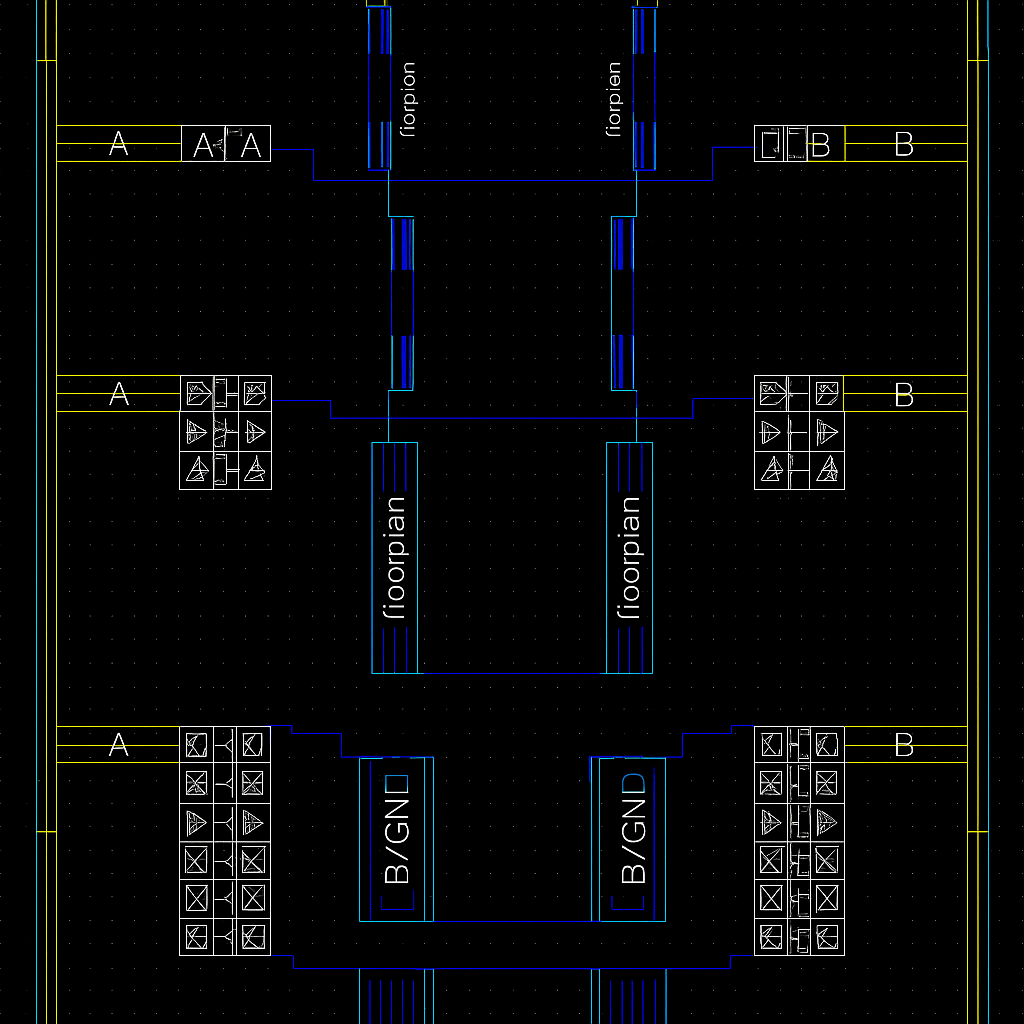

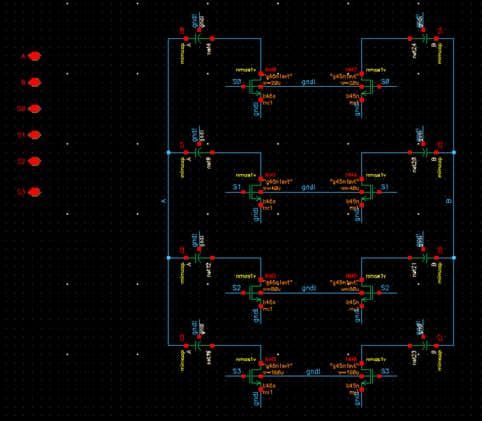

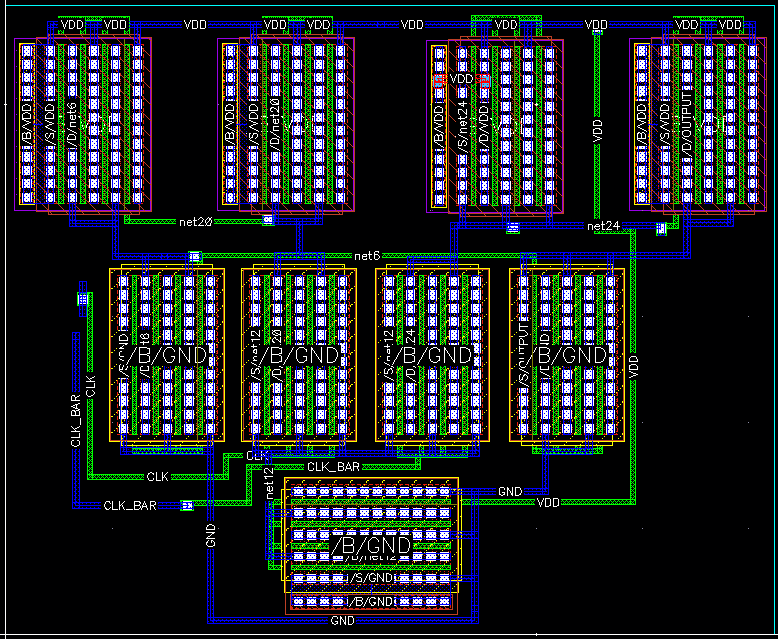

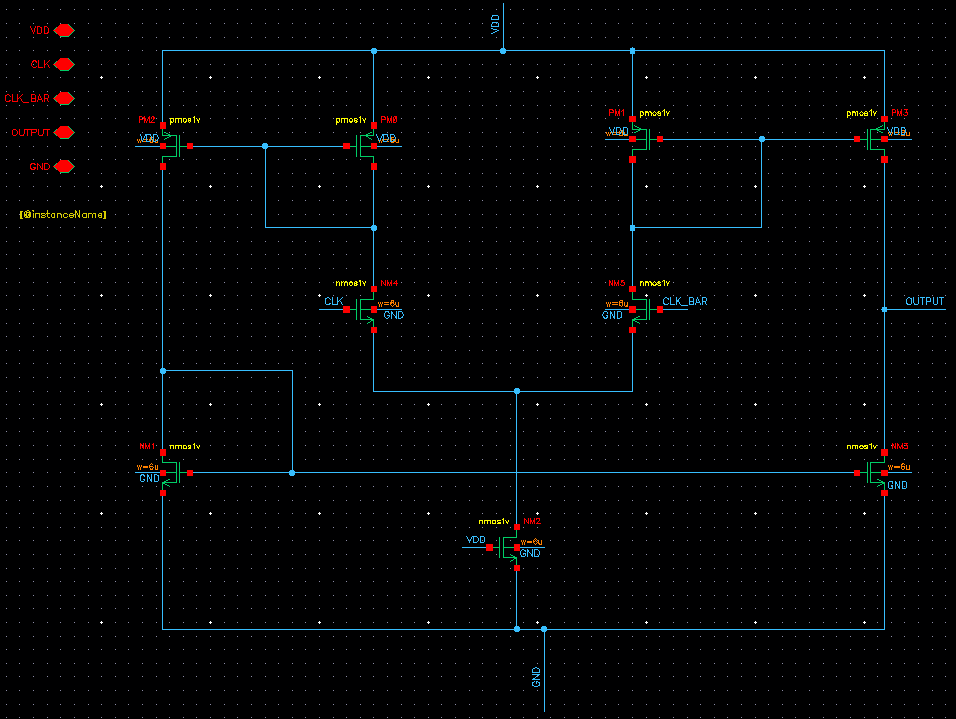

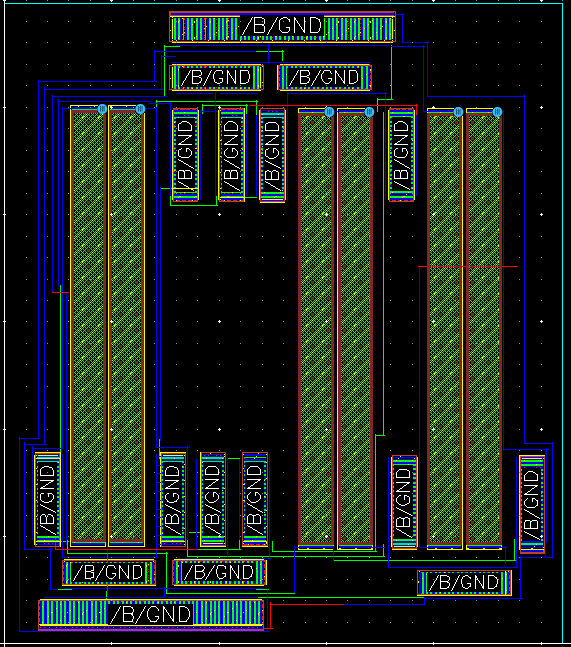

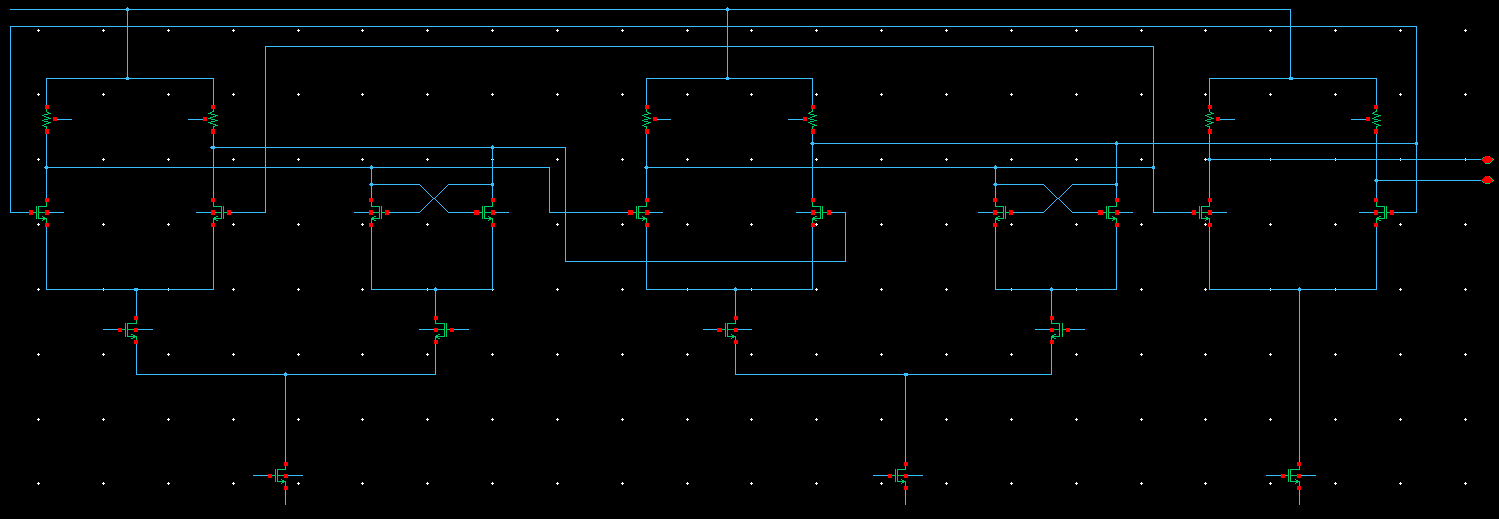

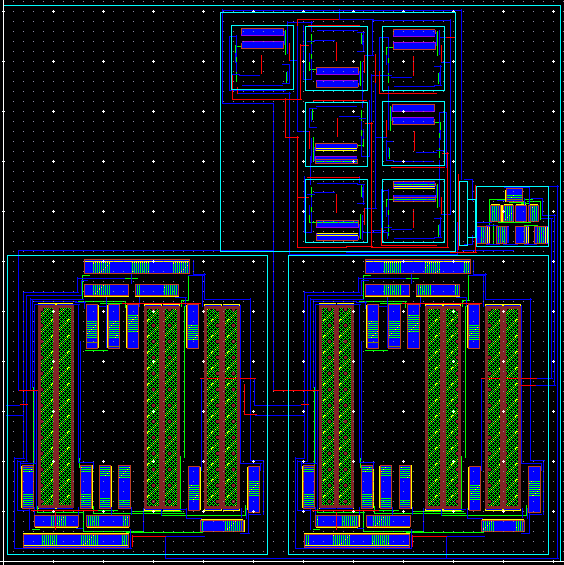

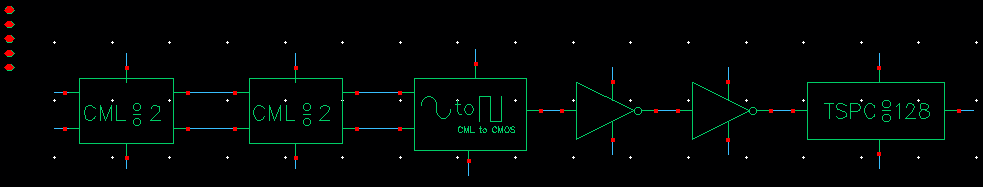

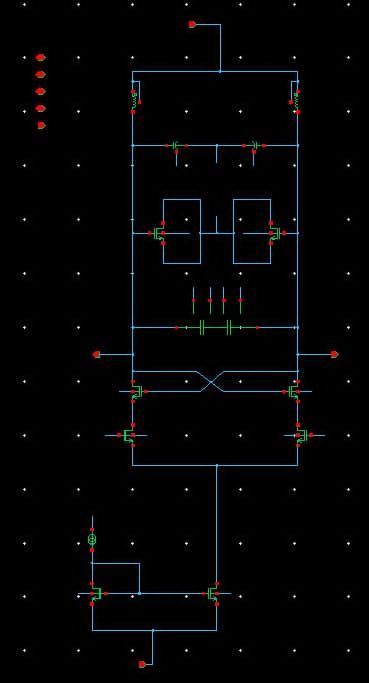

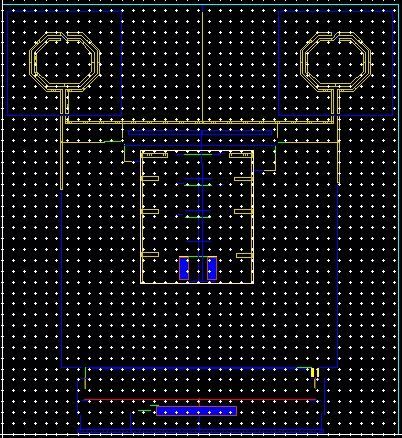

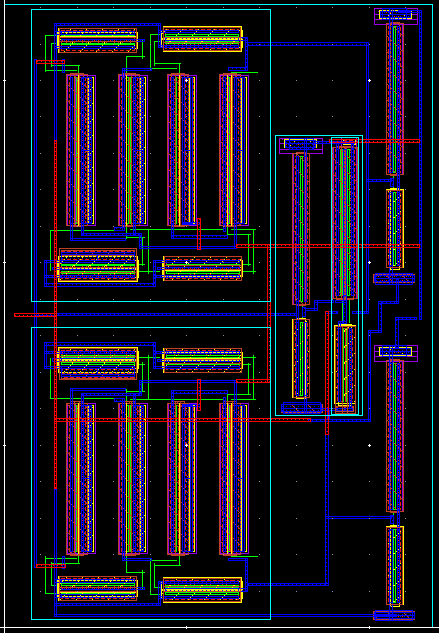

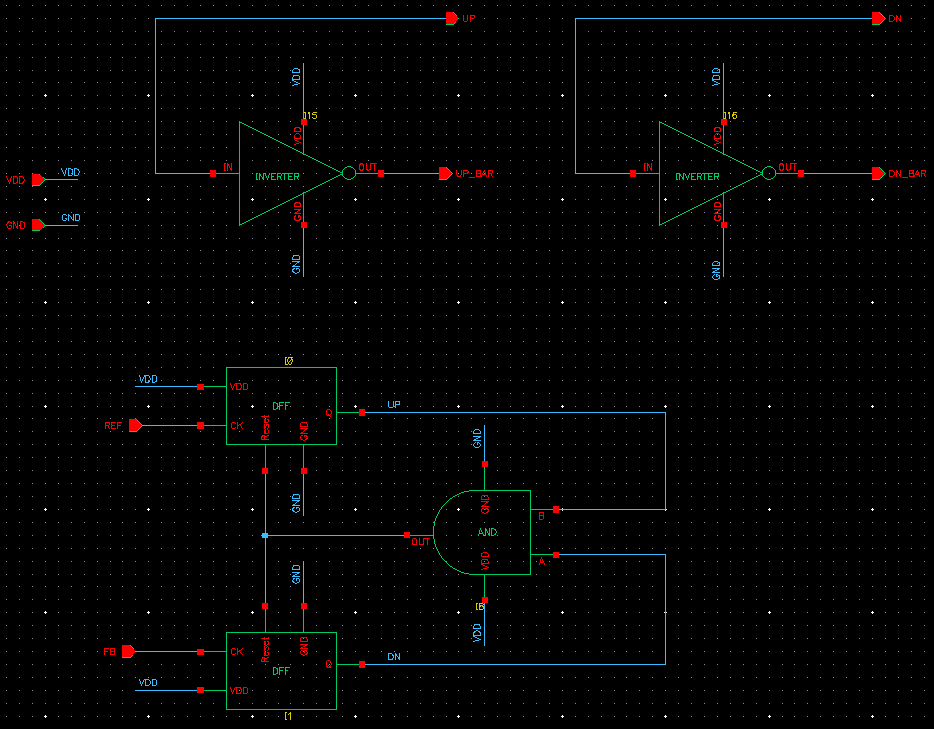

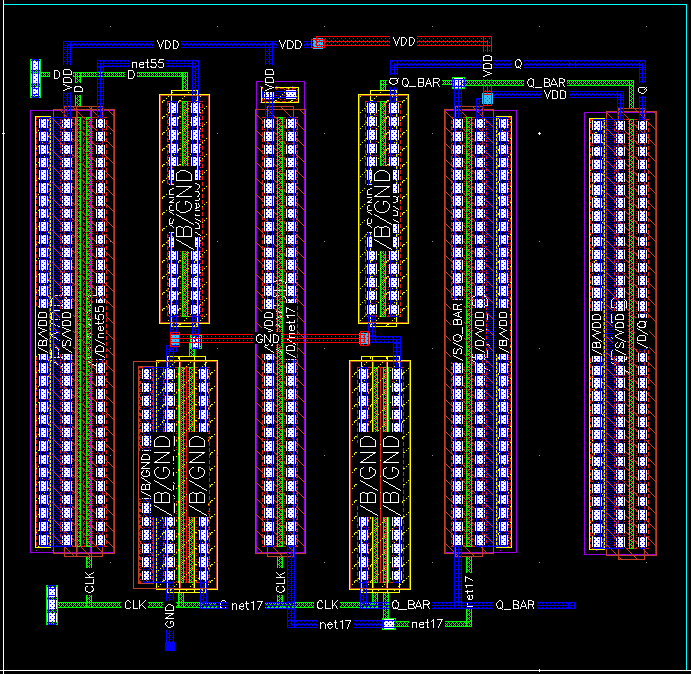

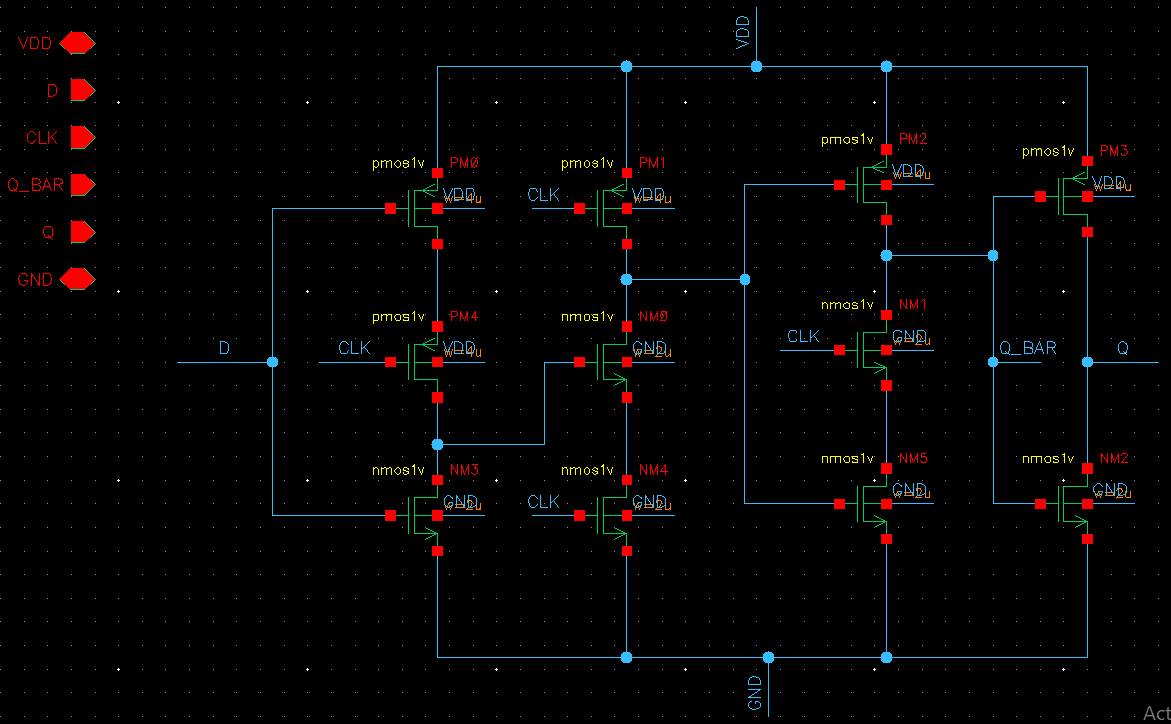

This project develops a low-noise phase-locked loop (PLL), a circuit that locks an output signal to a stable reference, ensuring accurate frequency and phase alignment. The design covers all essential building blocks of a PLL, including the Phase Frequency Detector, Charge Pump, Loop Filter, Voltage-Controlled Oscillator, and Frequency Divider. Each block is optimized both at the circuit level and the layout level for maximum efficiency.

The target design achieves a frequency above 26 GHz, less than 150 femtoseconds of jitter (a measure of timing uncertainty), under 30 mW of power consumption, and an active chip area below 0.4 mm². This combination provides compact, energy-efficient solutions for 5G applications.