DEVELOPMENT ON CONFIGURABLE UVM-BASED VERIFICATION PLATFORM FOR PCIE 4.0 SUBSYSTEM THAT SUPPORTS DIFFERENT CONTROLLER

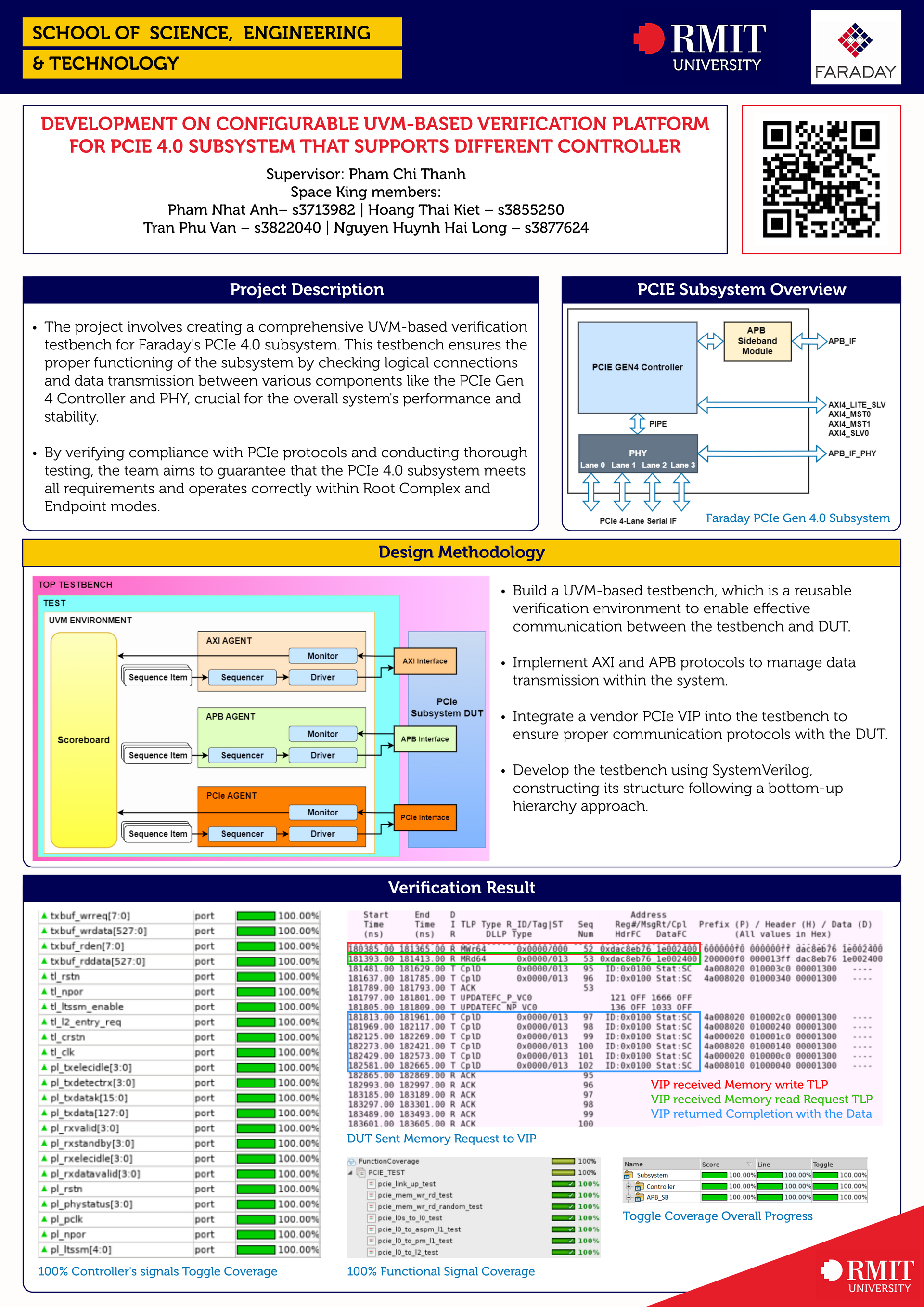

Faraday's PCIe 4.0 subsystem is a crucial component of a larger SoC design, connecting various IPs like the PCIe 4.0 Controller and PHY Controller. The primary objective of this project is to develop a robust and reliable Universal Verification Methodology (UVM)-based verification testbench for the PCIe 4.0 subsystem. The goal is to ensure the subsystem meets all requirements and functions correctly in both root complex and endpoint modes, including support for PCIe generations 1, 2, 3, and 4.

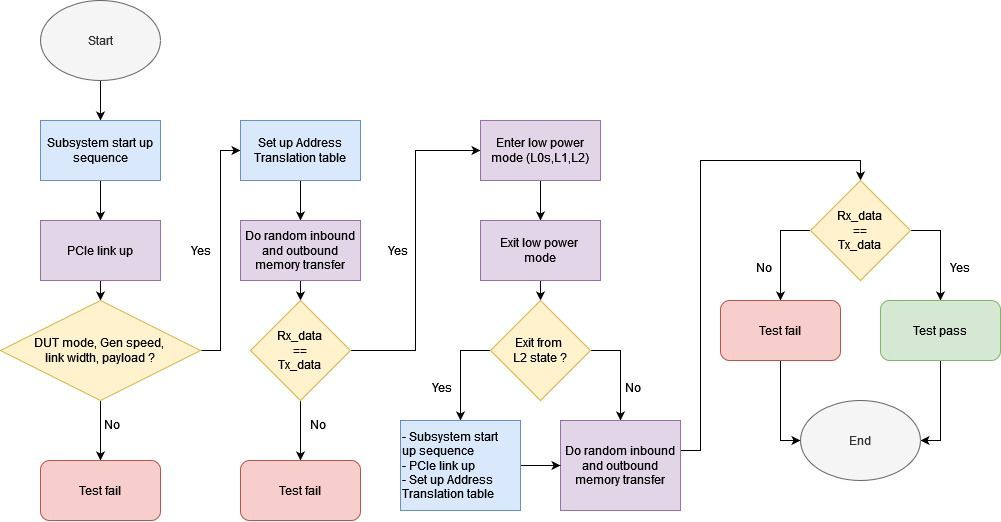

The focus of the project is on verifying the PCIe specifications and features, particularly the stages of link training, memory transfer, and low power state transition. The team has developed a UVM-based verification environment that can generate various sequences and display results on a scoreboard, allowing them to validate the functionality and reliability of the design. In addition, the sideband module will be validated by using APB to access the internal register. A regression, which includes all types of functional tests, will be run to ensure the subsystem works reliably in various conditions.

The verification environment built in this project can be reused in future projects with minimum adjustment, thanks to the modularity, reusability, scalability, and flexibility of the UVM framework. This ensures that the investment in developing the testbench will continue to pay dividends in future projects, as the team can leverage the existing testbench and build upon it to address new challenges.