Achieving Design Excellence - Practical of Verification in IC Design: Development of UVM Verification Testbench for SuperSpeed USB Dual Role Subsystem

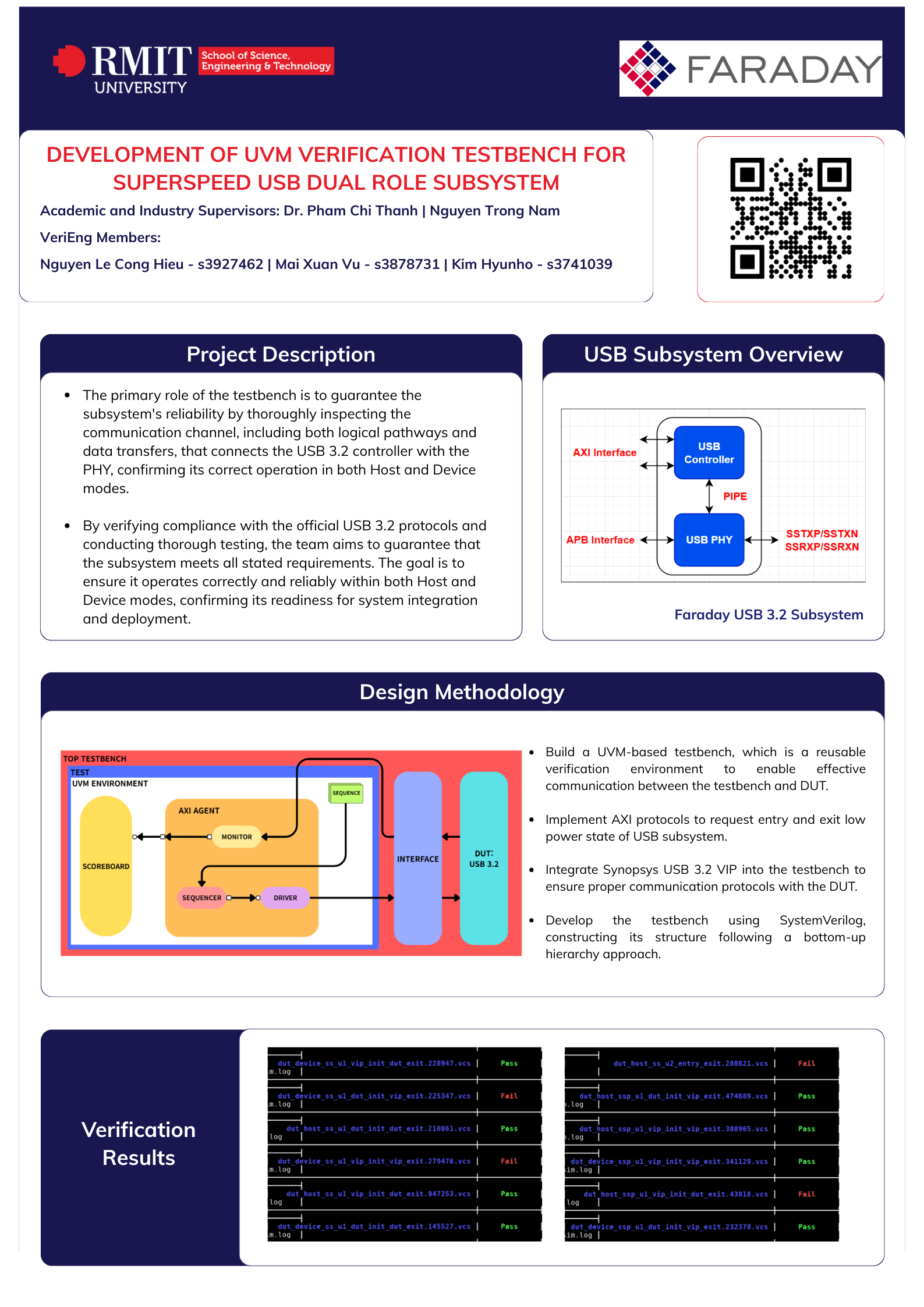

The USB 3.2 subsystem, which integrates the Controller and PHY, is a critical IP in modern SoCs. This project’s objective is to develop a comprehensive Universal Verification Methodology (UVM) testbench for its validation. The central goal is to guarantee the subsystem meets all specifications, with critical emphasis on its flawless operation in both Host and Device modes. This verification effort will ensure full support for USB 3.2 Gen 1 and Gen 2 data rates.

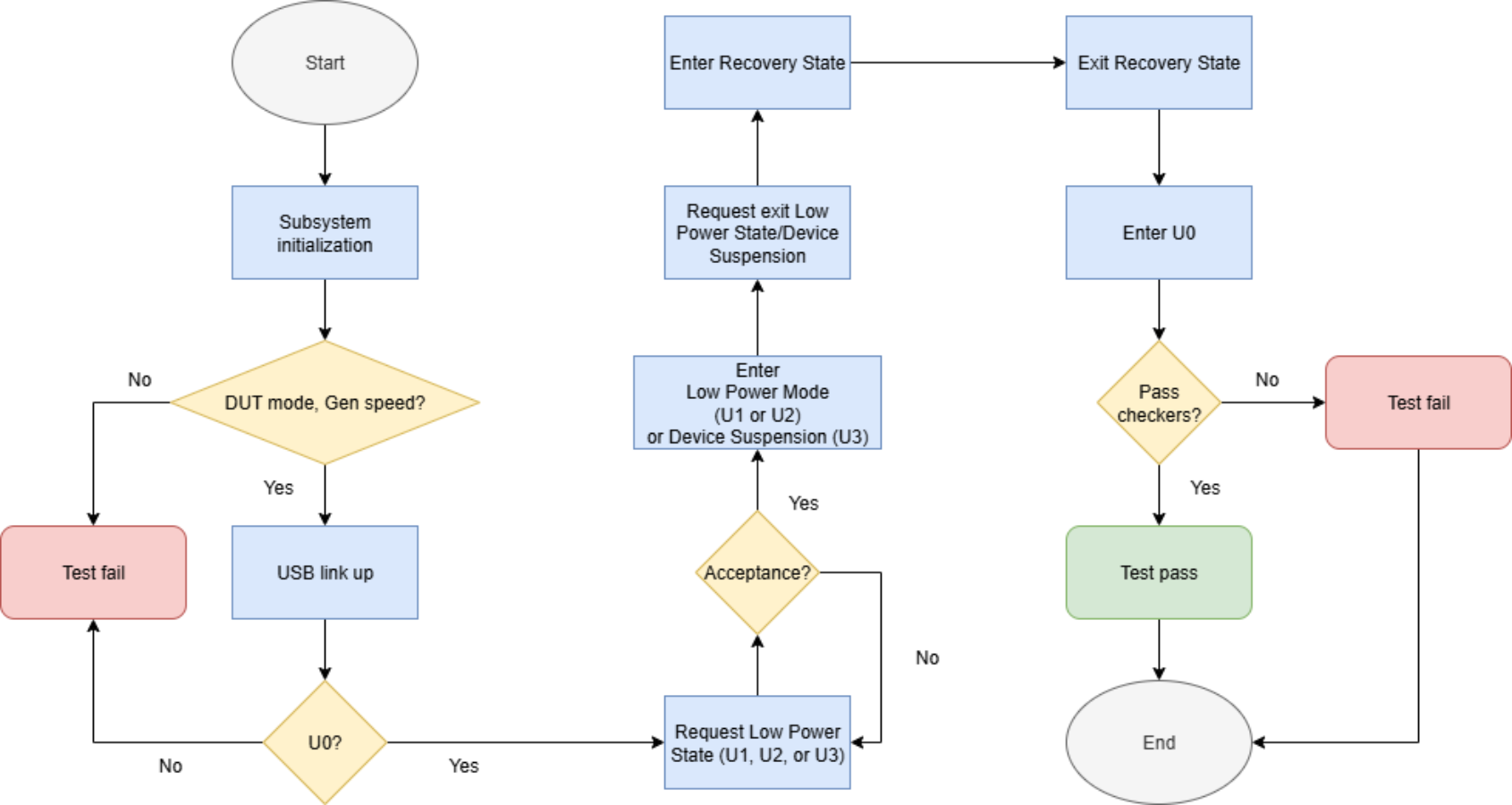

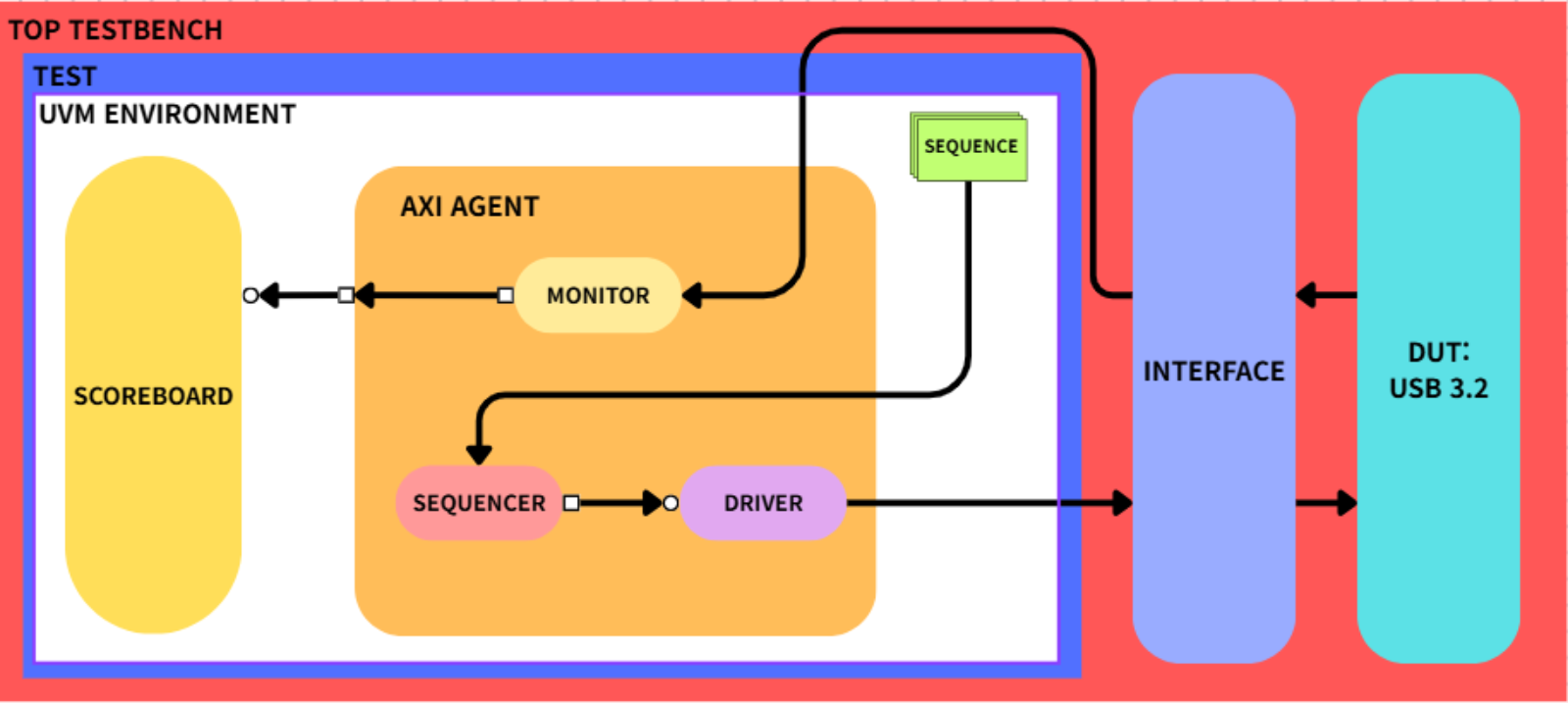

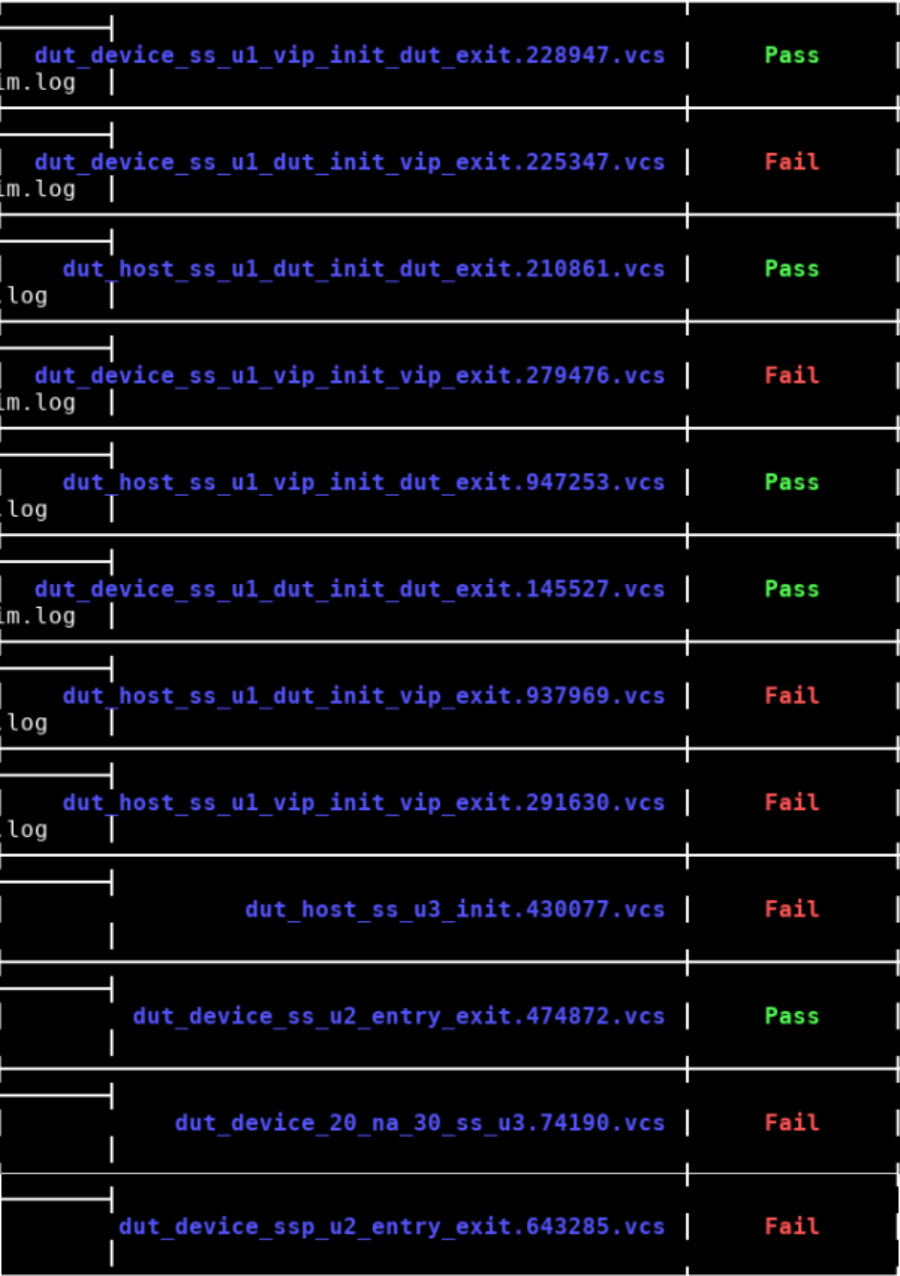

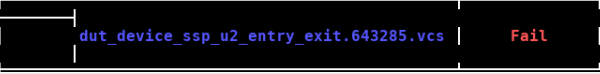

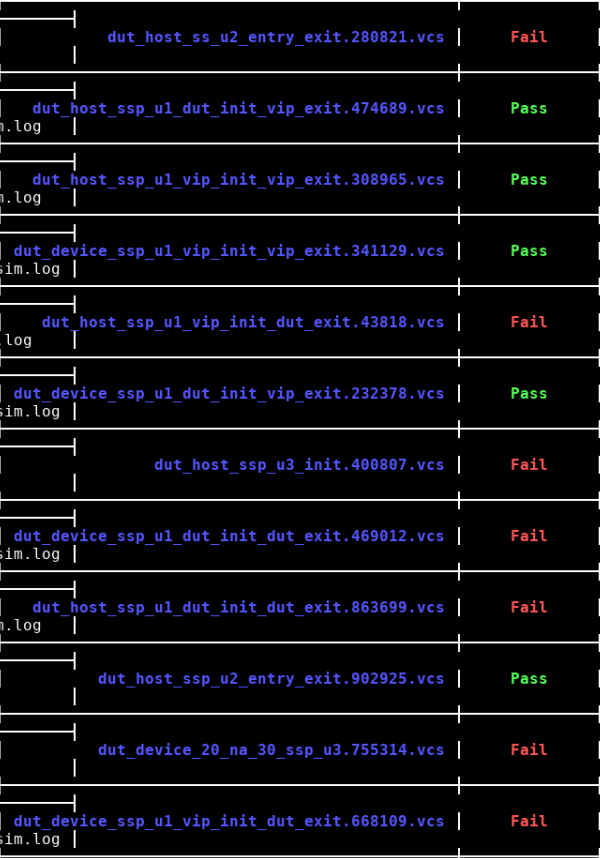

The project focuses on verifying core USB 3.2 features like link training, data transfers, and low-power state transitions. The UVM environment will use diverse stimulus sequences and a scoreboard to validate functionality, while an AXI interface will verify internal registers. A comprehensive regression suite will be run to ensure the subsystem operates reliably under all specified conditions, confirming its robustness and stability.

The verification environment, based on the UVM framework, functions like a set of standardized, reusable building blocks. This modular design means the entire structure does not need to be rebuilt for new projects. Instead, existing components can be reused as needed, making future development significantly faster and more efficient.